酷睿Ultra 200V内核解密:四个E核略大于一个P核

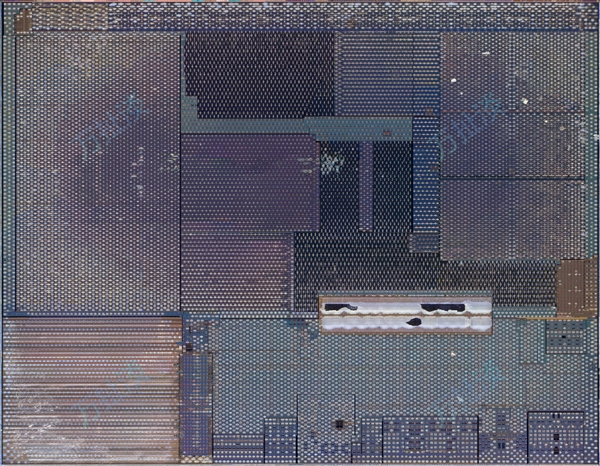

国外硬件专家Nemez利用B站网友的“狗屁”底图,对Core Ultra 200V系列处理器Lunar Lake的内部结构布局进行了详细分析。大小核心的分布很有趣。

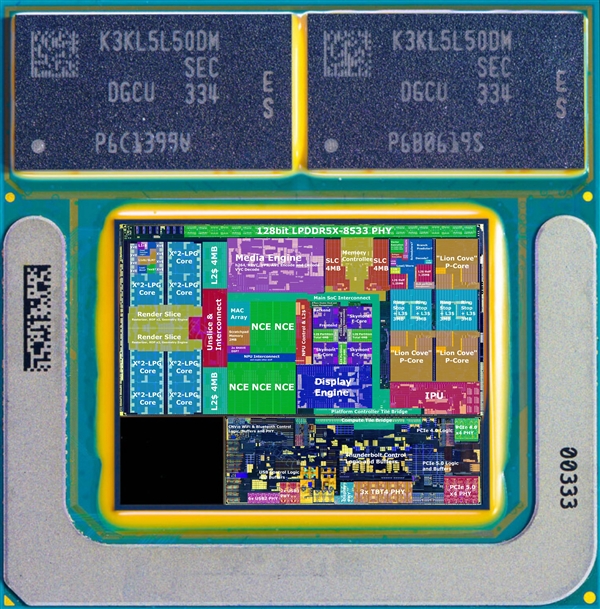

酷睿Ultra 200V处理器分为计算模块、平台控制器模块,分别采用台积电3nm、6nm工艺,共同放置在台积电22nm制造的基底上。计算模块区域为16.278.58139.60平方毫米,平台控制器模块区域为11.513.9745.69平方毫米,基础区域为16.7713.10219.69平方毫米。

计算模块

平台控制器模块

根据

它的另一大特点是搭载了两颗LPDDR5X内存,有助于节省主板面积和笔记本空间,使其更薄更轻或者放入更大的电池。它还有助于提高系统通信性能,减少延迟,极大地提高系统通信性能。降低整体功耗。

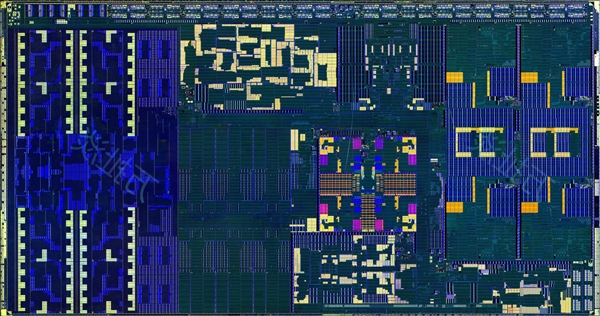

从分析图可以看出,四个Lion Cove架构的P核位于计算模块的右侧边缘,中间夹着共享的12MB三级缓存,并分为四块,每块3MB。的每个核心都有自己的2.5MB L2缓存,同样分为两个块。

旁边是四个为一组的Skymont架构的E核,集体共享12MB二级缓存,分成了三块。比较,四个E核的面积稍微大于一个P核,这无疑是颇为值得称道的,因为上代四个E核面积约等于一个P核,而这一代E核的IPC性能整数提升了38、浮点提升了68,但面积却没有明显增大。

再左边是NPU AI引擎,分为六组NCE MAC阵列。推测每个组都有2MB 缓存。

左边缘是GPU核心显示,共有八个Xe2 LPG架构核心,以及分为两块的8MB二级缓存。

还有媒体引擎、显示引擎、8MB SLC系统缓存和128位LPDDR5X-8533内存控制器。

平台控制器模块包含PCIe 4.0/5.0控制器、Thunderbolt控制器、USB 3.x/2.0控制器、Wi-Fi和蓝牙控制器等。