Intel Arrow Lake P/E大小核布局变了!有两大好处

快科技7月2日报道称,Intel的12/13/14代酷睿均为P/E混合架构设计,俗称大小核。整体布局是一样的,但是下一代Arrow Lake,也就是Core Ultra 200系列(没有15代酷睿)将会迎来变化。

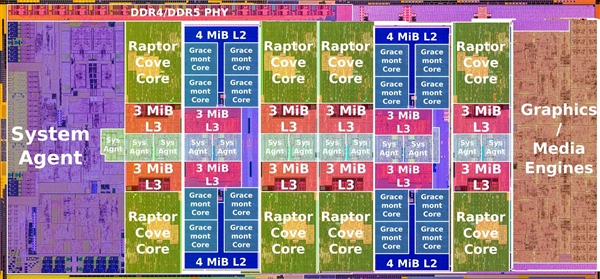

在目前的架构中,P核、E核、GPU核显、I/O控制器等亿次都挂靠在一条环形总线(Ring Bug),其中P核是一个整体(最多8个),E核是另一个整体(最多16个)。

目前还没有Arrow Lake(包括低功耗版本的Lunar Lake)的具体架构图,但有专家根据已知信息做了一个示意图如下:

P核、E核不再是独立的两部分,而是混合在一起,每一个P核的旁边是四个E核组成的集群,各有自己对应的三级缓存。

当在环形总线上通信时,它首先经过一个P核,然后是四个E核,然后是两个P核,然后是四个核,最后是一个P核,依此类推。

这样做似乎有两个优点。一是P核、E核之间的通信延迟会大大缩小可直接通话,无需隔几站。

例如,当线程调度器需要将不同的负载分配给不同的P核和E核时,或者当某个负载需要在P核和E核之间转移时,效率会高很多。

二是改善散热,更加均衡。

比如,在游戏等高负载场景下,P核将不再被密集使用,导致该区域集中发热,而E核则基本闲置。

当然,具体的Arrow Lake架构设计还需要等到发布才能挖掘出更具体的信息。

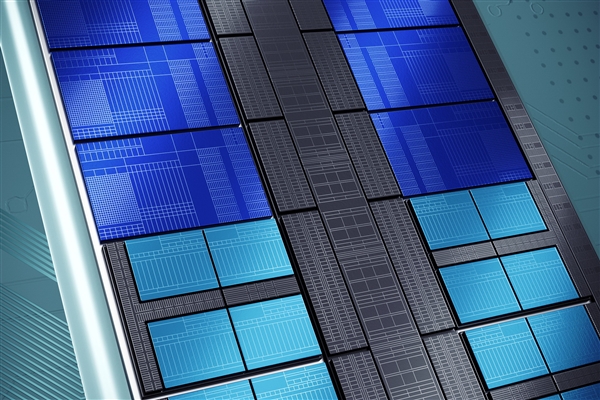

在现有架构中,深蓝色代表大核心,浅蓝色代表小核心集群。