3D闪存哪家强:姜还是三星的辣 长江仅次之

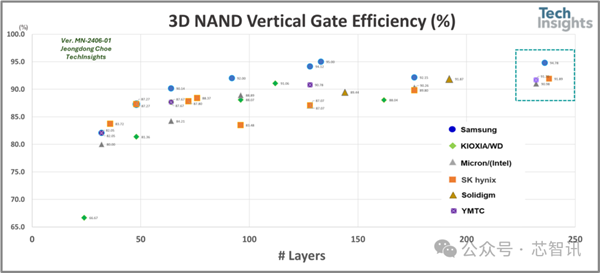

近日,市场研究机构Techinsights对三星、SK Hynix/Solidigm、美光、铠侠(西部数据)、长江存储等厂商的200层以上3D NAND Flash进行对比分析,发现三星的垂直单元效率(VCE、垂直单元)效率) ) 是最高的。

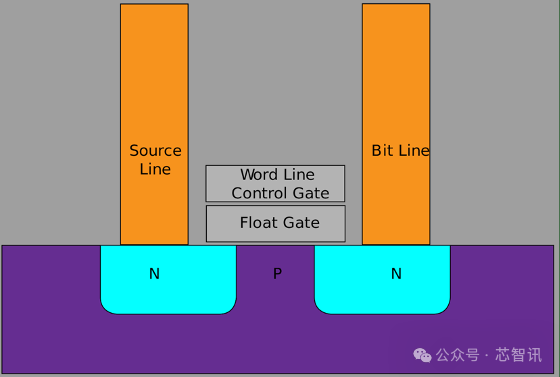

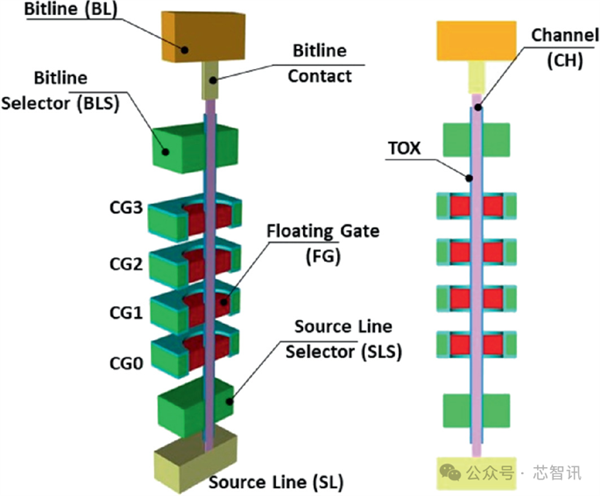

传统的NAND闪存单元采用平面晶体管结构,包括控制栅极(Control Gate)和浮动栅极(Float Gate)。通过向单元施加电压,电子在浮栅中被存储和移除。

多年来,供应商已将平面NAND 的单元尺寸从120nm 缩小到1xnm 节点,容量增加了100 倍。

然而,当单元尺寸达到14nm的极限时,这意味着该技术不再具有可扩展性。因此,NAND 制造商转向3D NAND,以实现超过2D NAND 结构的数据密度,并能够在新一代技术节点上运行。生产。

具体是平面 NAND 由带有存储单元的水平串组成,而在 3D NAND 中,存储单元串被拉伸、折叠并以“U 形”结构垂直竖立。

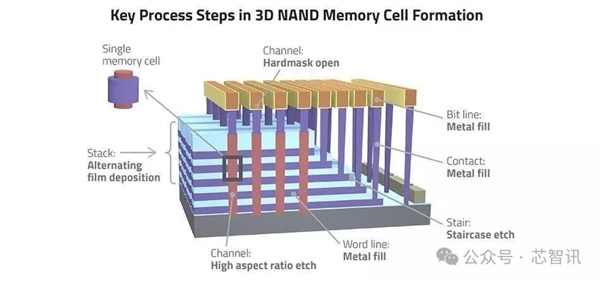

实际上,单元按比例密度垂直堆叠,因此存在多个级别的3D NAND 存储单元。

3D NAND的层数描述了堆叠在一起的字线(Word Line)数量。在这些字线层上切出一个垂直柱,柱子与每条字线的交点代表一个物理单元。

也就是说,每个3D NAND 存储单元都类似于一个微小的圆柱形结构。

每个微小单元由中间的垂直通道和结构内部的电荷层组成。通过施加电压,电子可以移入和移出绝缘电荷存储膜,然后可以读取信号。

平面NAND 减少了每个节点的单元尺寸,3D NAND 则采用了更宽松的工艺,大约在 30nm 到 50nm 之间。

3D NAND存储器容量的扩展主要是通过增加垂直层数来实现的。在这种3D NAND 结构中,单元密度随着堆叠层数的增加而增加。

然后,每隔一到两年,供应商就会从一代技术迁移到下一代技术。

据研究数据,供应商平均每代 3D NAND 都会增加 30% 至 50% 的层数,而每一代新的芯片将会增加 10% 至 15% 的晶圆成本。这也使得NAND 的每bit成本能够平均以每年约20%幅度降低。

现在200层以上的TLC NAND产品已逐渐成为主流,如三星236层NAND 、SK 海力士 238层NAND、美光 232层NAND 、YMTC 232层NAND。

此外,还有一些厂商接近200层,例如铠侠和西部数据的112层/162层NAND以及Solidigm的144层/192层(FG)NAND。

Techinsights 从SK Hynix 2TB SSD PC811 HFS002TEM9X152N(设备:H25T3TDG8C-X682)中提取了SK Hynix 238L 512 Gb 3D NAND 芯片。芯片尺寸为34.56mm2,位密度为14.81Gb/mm2。

当谈到3D NAND 单元效率时,垂直单元效率(VCE) 对于NAND 单元工艺、设计、集成和器件操作非常重要。

随着堆叠栅极总数的增加,单元VC(垂直单元)孔高度也增加。

降低VC高度和纵横比的方法之一是通过减少虚拟栅极(dummy gates)、通过栅极(passing gates)和选择栅极(select gates)的数量来提高垂直单元效率。

垂直单元效率可以定义为活动单元占总门数的百分比,其计算方法是将活动WL(字线)除以集成门总数。

垂直单元效率越高,制程集成度越高,长宽比越低,整体效率越高。

VCE可以定义为活动单元与总门数的比率,即活动WL的数量除以集成门总数x 100%。

例如,NAND串由有源WL、通道WL(包括虚拟WL)和选择器(源极/漏极)组成。

如果包含96 个Active WL,总共115 个门,则VCE 为83.5%,计算为96/115100%。

VCE越高,越有利于工艺集成,实现更低的长径比和更高的生产效率。

Techinsights 发现,他们最新的多层V-NAND在多代 3D NAND 产品中,三星始终以最高的垂直单元效率领跑行业。拥有令人印象深刻的垂直单元效率,建立在前几代产品在效率方面享有盛誉的基础上。

美光和YMTC也在其产品中展示了强劲的垂直单元效率数据,反映了他们在减少虚拟栅极、传输栅极和选择栅极数量以优化垂直单元效率方面取得的重大进展。

3D NAND垂直单元效率趋势

综上所述,三个星每一代产品的VCE都是最高的,比如采用单层结构的128层是94.1%,176层COP V-NAND是92.1%,236层2nd COP V-NAND是94.8% 。

YMTC的232层Xtacking 3.0的VCE是91.7%,美光232层是91%。

Kioxia 162 的VCE 稍低一些,为88%。

SK海力士在238层共有259个门,VCE为91.9%,仍低于三星的236L。